- Startseite > Produkte > Starre Leiterplatte > Über In Pad Leiterplatte

Die Idee des IoT (Internet der Dinge) wird immer beliebter, heutzutage kann alles mit dem Internet verbunden werden.Tragbare Geräte, die Menschen täglich anziehen oder herumtragen, müssen jedoch so klein wie möglich sein.

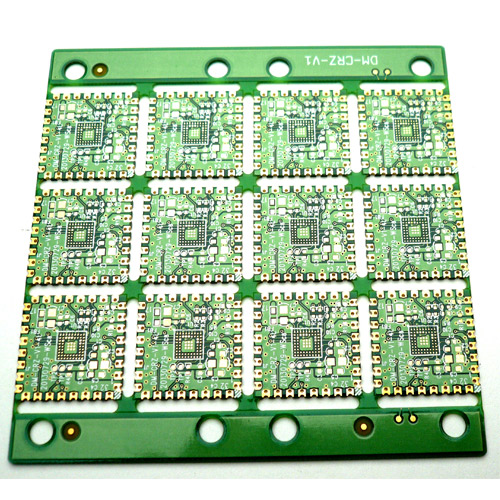

Um die Größe der Leiterplatte zu verringern, bietet PCE unseren Kunden den Via in Pad-Prozess an.Wir füllen die PTHs (Plated Through Holes) mit leitendem (oder nicht leitendem) Epoxid und verkupfern die Oberfläche jedes Durchgangslochs.

|

|

|

|

|

Anwendungen & Nutzen:

- Engere BGA-Abstände

- Erhöhte Wärmeableitung

- Reduzierte Schichtanzahl oder Platinengröße, was letztendlich die Kosten senken kann

- Verbesserte Routing-Dichte (höhere Dichte pro Schicht)

- Verstärkung des Pad-Aufsatzes

- Ermöglicht Hochfrequenzdesigns den kürzestmöglichen Weg zur Umgehung von Kondensatoren

- Überwindet Designprobleme und Einschränkungen bei hoher Geschwindigkeit wie niedrige Induktivität

Starre Leiterplattenkapazität

| Features | Fähigkeit | |

|---|---|---|

| Laminierung | Schichtenanzahl | 1-32 Schichten |

| Min.Dicke | 4 mil (0,1 mm) | |

| Maximale Größe des Arbeitsfelds | 24x31.5 mm (610x800mm) | |

| Max.Seitenverhältnis | 10:1 | |

| Kupfer | Kupferdicke | 0.33 bis 3.0 Unzen (11 bis 105um) |

| Trace | Min.Linienbreite / Leerzeichen | 3/3 mil |

| Routing | Maßtoleranz | +/- 2 mil (0.05mm) |

| Lötmaske | S / M Mindestdammbreite | 2.5 mil |

| Impedanzkontrolle | Differentialpaar | +/- 10% |

| Mechanisches Bohren | Min.Bohrlochgröße | 4 mil(0.1mm) |

| 3 Achsen | Genauigkeit der Tiefenkontrolle | +/- 2mil (0.05mm) |

| Materialverfügbarkeit | FR-4, Hoher Tg FR-4, halogenfreies FR-4, Metallkern, Niedriger Dk / Df (ISOLA / Rogers) | |

| Oberflächenbehandlung-Verfügbarkeit | Bleifreies HASL, HASL, OSP, ENIG, Mustervergoldung, Eintauchen in Silber / Zinn, Carbon Ink | |